# ORWAY CORPORATION

# Nuclear Instrumentation Laser Metrology

27 BOND STREET, WESTBURY, NEW YORK 11590, U.S.A.

TEL. (516) 997-8120

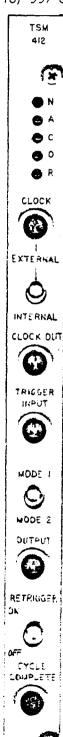

MODEL 412

TIMING AND SEQUENCE MODULE

**FEATURES**

PROGRAMMABLE PULSE TRAIN

MODE 1: Variable pulse interval

MODE 2: Variable pulse width and interval

REPEAT CYCLE COUNTER

1K x 24BIT PROGRAM MEMORY

This general purpose module provides a serial sequence of time related pulses. Two modes are available; Mode 1 Output consists of fixed width pulses with pulse separation determined by a stored program; Mode 2 Output consists of a pulse train with both the pulse width and pulse spacing determined by a stored program. In either mode the output sequence can be made to occur continously or under the control of an external trigger. In addition a programmable Recycle Counter is available to generate from 1 to 255 repetitive sequences. A 24 bit by 1024 word memory provides for 1024 set times. The module clock may be selected as external front panel input or via the dataway P2 line. Module Inputs are optically isolated for improved system connections.

MODE 1. A serial pulse train will be generated at the module Output port with pulses nominally one microsecond wide. Each pulse can be programmed at any fixed time (Set Point) up to 16,777,214. The pulse train will be generated after the module is enabled and triggered. A Cycle Complete Output pulse will occur at the completion of the last programmed pulse in the sequence.

MODE 2. After Reset, Z, C or the module being enabled, the Output port will be logic 0. After being triggered and reaching the first set point the Output port will become logic "1". The next set point will change to logic 0 and the process continue until the last set point is reached. Up to 512 pulses with variable spacing and width can be generated.

SET TIME LOADING. Set Times consist of a 24 bit number set in increasing time up to a maximum of 16,777,214. Times must not be set less than 2 microseconds increments. A setting of 16,777,215 at any point is used to indicate end of sequence and will terminate the pulse train at fewer than the maximum number.

RECYCLE MODE. A recycle register can be loaded with any number from 0 to 255. A zero will result in the module continually generating the sequence after being triggered until reset or disabled. Other numbers will result in N repeats of the sequence after being triggered.

RETRIGGER MODE. Selecting the Retrigger mode will result in the module being armed to be triggered again after the sequence or N recycles sequences are completed. Selection of Retrigger off will result in the module being disabled at the end of a sequence.

#### DA'

Q

| ATAWAY COMMANDS  |                                                                                                                                                                                 |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| F(0)A(0)         | Read Set Point onto dataway R1 thru R24 with LSB on R1. Increment Memory Address.                                                                                               |  |  |  |  |  |

| *F(0)A(1)        | Read Statis Register onto dataway.  Bit 1 1=Enabled                                                                                                                             |  |  |  |  |  |

| *F(0)A(2)        | Read Memory Address onto dataway R1 thru R10 with LSB on R1.                                                                                                                    |  |  |  |  |  |

| *F(6)A(0)        | Read Module Number onto Dataway, Decimal 412.                                                                                                                                   |  |  |  |  |  |

| F(16)A(0)        | Write Set Point into memory from dataway write line WI thru W24 with LSB on W1. Increment Memory Address.                                                                       |  |  |  |  |  |

| F(16)A(1)        | Write numbers of cycles into Recycle Register from data-<br>way W1 thru W8 with W8 as LSB. Zero written into stor-<br>age results in continous recycle until disabled or reset. |  |  |  |  |  |

| F(16)A(2)        | Write Address ino Memory Address Register from dataway write lines Wl thur WlO with LSB on Wl.                                                                                  |  |  |  |  |  |

| *F(24)A(0)       | Disable unit. Stops module cycle and leaves output in last state. Mode 1 Output pulse will finish if output has started when command was executed.                              |  |  |  |  |  |

| F(26)A(0)        | Enable unit. Enables unit for triggering. Clears Mode 2 Output & Complete Output and resets Memory Address to zero.                                                             |  |  |  |  |  |

| *C÷Z or POWER UP | Disable unit, clear Mode 2 and Complete Output, Set Memory Address to zero and set Recycle Register to zero.                                                                    |  |  |  |  |  |

| Σ                | Dataway X=1 for all above commands,                                                                                                                                             |  |  |  |  |  |

|                  |                                                                                                                                                                                 |  |  |  |  |  |

not be executed.

Dataway (=1 for all above commands when module is disabled. When module is enabled (=1 only for commands marked with \* which will be accepted. All others will

### 1.0 Abstract

This specification, in conjunction with referenced documents, sets forth all characteristics of the subject module. This specification shall take precedence where areas of overlap with the referenced documents occur. The intended use of this document is to provide a minimum design goal for the module as well as a working document for subsequent users.

### 2.0 Reference Documents

- 2.1 Standard Timing Pulse, TFTR-10A2-H57.

- 2.2 IEEE Standard Modular Instrumentation and Digital Interface System (CAMAC), IEEE Std. 583-1975.

- 2.3 Reliability, Quality Control and Temperature Cycling, TFTR-10A2-H58.

- 2.4 Printed Circuit Board Fabrication and Assembly Specification, TFTR-10A2-H54.

- 2.5 Printed Circuit Artwork Specification, TFTR-10A2-H53.

- 2.6 Electronic Schematic Specification, TFTR-10A2-H55.

- 2.7 Quality Assurance Plan, TFTR-9A1-002.

- 2.8 TFTR Cable and Connector Definition, TFTR-9C12-015.

# 3.0 Introduction

The Timing and Sequencing Module is a general purpose dual mode device, designed to provide a serial sequence of time related trigger or variable width pulse outputs. In Mode 1 the output is a series of fixed width pulses with the pulse-to-pulse separation determined by a stored program. In Mode 2 both the pulse-to-pulse separation and the pulse width are variable and are controlled by a stored program.

#### 4.0 Basic Features

In Mode 1 a serial data stream of up to 1024 pulses shall be available at the output port. Each pulse shall have a nominal pulse width of one microsecond and shall conform to the specification in section 6.3. The pulses shall be programmed to occur at any fixed time up to 16,777,214 clock interval after the module is triggered. Once the module has been triggered it shall ignore all other input trigger pulses until the last requested pulse has been completed. A Cycle Complete output pulse shall be produced immediately after the completion of the last programmed pulse (see 11.4).

# √ 4.2 Mode 2

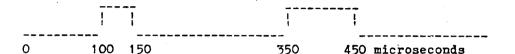

Mode 2 differs from Mode 1 in that the output pulse width is variable. Within 500nanoseconds of reset or the module being enabled, the output shall be a logic 0. When the first set point is reached the output shall switch to a logic 1 state. When the next set point is encountered the output shall switch to a logic 0 state. This cycle shall continue until the last set point has been reached. Up to 512 output pulses, each of which has a variable pulse width shall be allowed. The pulse width resolution is 1 clock interval. As an example, with the following times loaded (using a 10 microsecond clock):

| Address | Number Loaded | Time(microseconds) |

|---------|---------------|--------------------|

| 0       | 10            | 100                |

| 1       | 15            | 150                |

| 2       | 35            | 350                |

| 3       | 45            | 450                |

With the 10 microsecond clock, the mode two output waveform would be:

The selection of mode 1 or mode 2 shall be via a front panel switch.

The position of this switch shall be available to the CAMAC bus in the status word.

#### 4.3 Clock

It shall be possible to use this module with a dataway clock (line P2) or with an external clock. The clock source shall be selectable by a front panel switch. The position of this switch shall be available to the CAMAC bus in the status word.

#### 4.3.1 Dataway Clock

The dataway clock will operate at a nominal frequency of 1 MHz. The dataway clock will appear on dataway line P2 with signal levels corresponding to the CAMAC standard (reference 2.2). It shall be possible to divide this clock frequency by factors of 1, 10, or 100 by an internal adjustment. The selected dividing ratio will be obtainable by reading the status word. The dataway clock frequency will vary from 800 KHz to 1.5 MHz and will have a maximum rate of change of 500 KHz/sec. The clock waveform will be a rectangular pulse with a duty cycle between 50/50 and 60/40. The module shall operate as specified under these conditions of clock variation.

### 4.3.2 External Clock

If an external clock is used, the Clock Out connector shall provide a buffered version of the external clock as divided, with a

100 nanosecond maximum delay when loaded as shown in 11.2.2. The maximum external clock rate will be 1.0 MHz, with an acceptable clock waveform duty cycle of 10% to 90%. The electrical characteristics of this input are described in 6.2. The external clock shall be divided by the same internal divider as the dataway clock.

The module shall contain a 24 bit wide by 1024 word long memory which is used to store the 1024 set times. Each of the output pulses is associated with a number from 0 to 1023 corresponding to the address of the setting in the memory. During the timing cycle the memory address shall be provided on the rear panel auxiliary connector (see 6.3 and 11.2) in binary form which allows the user to determine which pulse is occuring. On the trailing edge of the Mode 1 output pulse the address output at this connector shall be changed to the number of the next output pulse. In Mode 2 the address shall be changed 1 microsecond after the leading edge and trailing edge of the output pulse. If all 1024 output pulses are used, the address on the auxiliary connector will be zero after the final pulse.

#### 4.5 Set Time Loading

This system shall have a resolution of 1 clock period and a maximum time of 16,777,214 periods. Each time setting requires a 24 bit binary number. The set times will be in order of increasing time. If an external clock operating at greater than 500 kHz is used, at least two microseconds between consecutive output time settings must be provided, for example: 10.000000---10.000002 seconds. If this condition is not met the results will be unpredictable. If the

external clock is operating at less than 500kHz the set times can be separated by only one clock interval.

# 4.6 Number of Output Pulses

It shall be possible to use fewer than the maximum number of output pulses. If fewer than the maximum number of set times are to be used, a word of all ones will be loaded into the memory after the final desired time setting. A time setting of all ones shall be a flag that the cycle is complete and not the value of 16,777,215 clock periods.

#### 4.7 Recycle Mode

The module shall be capable of retriggering itself at the end of each timing cycle. In this mode the number of cycles will be specified when the module is loaded. The maximum number of cycles shall be 255. If O cycles are selected the module shall retrigger indefinitely, until it is reset or disabled.

# 4.8 Trigger Input

ب<del>ر</del> د کرا The Trigger Input shall require a pulse of at least 500 nsec in duration. The electrical characteristics of this input are defined in 6.2.

#### 4.9 Cycle Complete Output

This output shall be a 1 microsecond wide pulse that occurs at the end of each cycle. This pulse shall occur less than 500 nanoseconds after the trailing edge of the final Mode 1 output pulse or 1.5 microsecond after the trailing edge of the Mode 2 output pulse (see 11.4). The electrical characteristics of this output are defined

in 6.3.

#### 4.10 Retrigger Mode

In the retrigger mode, on the falling edge of the last cycle complete output pulse the internal state of the module shall be reset so that the module may be triggered at a later time. The subsequent trigger will not occur until 1 microsecond after the falling edge of the cycle complete pulse, or it may be ignored. The retrigger mode shall be selectable by a front panel switch. If the retrigger mode is not selected an enable command must be issued before the module can be triggered.

# 4.11 Status Lights

4.11.1 N

The N light shall be illuminated when the module is addressed by the CAMAC N line. It shall remain on for a minimum of 0.1 seconds after the N line goes to a logic O.

4.11.2 A

The A light shall be illuminated when the module is enabled and ready to be triggered.

4.11.3 C

The C light shall be illuminated when the module has been triggered and is counting.

4.11.4 0

The O light shall be illuminated for a minimum of O.1 seconds when the output is high.

4.11.5 E

The R light shall be illuminated for a minimum of 0.1 seconds when a

module cycle is started, by the external trigger or when recycling.

### 5.0 Mechanical Characteristics

- 5.1 This shall be a standard single width CAMAC module as specified in reference 2.2.

- 5.2 This module shall conform to the mechanical requirements outlined in reference 2.2.

- 5.3 The electrical components of this module are to be mounted on a high quality flame retardent epoxy glass printed circuit board such as NEMA type FR-4 or equivalent. See references 2.4 and 2.5.

- 5.4 This module is to contain all necessary mechanical components, including metal covers, for insertion into a standard CAMAC crate.

See reference 2.2.

- 5.5 All components are to be identified with a standard manufacturer's part number or standard method of marking (e.g. resistor color code).

- 5.6 All electrical components are to be mounted on only one side of the board.

- 5.7 The condition of this module shall be monitored by front panel mounted LED's. The front panel shall be of aluminium and both sides are to have a conductive iridite finish. The color of the lettering shall be chosen to contrast with the panel finish and may be engraved or silk screened. See 11.1 for the suggested front panel layout.

- 5.8 The 36 pin card edge connector shall mate with a Viking 3V19 connector (or equivalent). The card edge connector shall be marked with pin 1 on top and pin 18 on the bottom on each side of the card. It is not necessary to mark each pin.

- 5.9 All components are to be assigned an identifying part name (e.g., R1, C2, etc.) which is to be cross-referenced to the manufacturer's part

number on the electrical schematic associated with this module. See reference 2.6.

5.10 All front panel connectors shall be 4 pin LEMO type connectors wired in accordance with the TFTR cable and connector specification (reference 2.8). The auxiliary output connector shall be wired as shown in section 11.2.

# 6.0 Electrical Characteristics

# 6.1 Input Power

- 6.1.1 This module shall conform to the electrical requirements outlined in reference 2.2.

- 6.1.2 Whenever possible, low power circuitry (such as CMOS or 74LS series) shall be used to minimize power dissipation.

- 6.1.3 The module shall derive its input power from the standard +/-24 volt and +/-6 volt CAMAC supply voltages.

- 6.1.4 The +6 and -6 volt supply voltages shall be bypassed on the module with electrolytic capacitors of at least 33 microfarads. The +24 and -24 volt supply voltages shall be bypassed with electrolytic capacitors of at least 6.8 microfarads. In addition, at least half of the integrated circuits shall contain ceramic bypass capacitors of at least 0.01 microfarads on their supply voltage lines. The 0.01 microfarad capacitors should be located as close as possible to the integrated circuits and distributed equally across the board.

#### 6.2 Input signals

All dataway signals are specified in reference 2.2. Other inputs shall be terminated with approximately 120 ohms, and shall be optically isolated from the module (see 11.3 for a typical input

stage). Non-dataway inputs shall be a minimum of 3.5 volts into the rated load. The Trigger Input shall be capable of being triggered by a TFTR standard timing pulse (reference 2.1).

# 6.3 Output Signal Characteristics

The Clock, Cycle Complete, Mode1/Mode2 outputs and the auxiliary connector outputs shall be differential and shall be capable of driving 120 ohms (see 11.2.2 for a typical output stage). The differential output voltage shall be at least 3.5 volts into the rated load. A HCPL-2601 optically coupled line receiver, in the module to be controlled, is recommended. The Mode 1, Cycle Complete and Clock Out outputs shall have the same timing characteristics as the TFTR standard timing pulse. The Mode 2 output shall have the same rise and fall times as the TFTR standard timing pulse.

# 6.4 CAMAC Protocol

6.4.1 Load address register

A(2).F(16).Write

Address on lines W1-W10 with LSB on W1.

6.4.2 Read set point and increment address

A(0).F(0).Read

Set point read on R1-R24 with LSE on R1.

6.4.3 Write set point and increment address

A(0).F(16).Write

Set point on W1-W24 with LSB on W1.

#### 6.4.4 \* Disable unit

A(0).F(24)

This stops the timing cycle and leaves the outputs in whatever state they were in when this command was executed. In Mode 1 the pulse output shall finish and then remain in the logic 0 state. In Mode 2 the output shall not change state.

#### 6.4.5 Enable unit

A(0).F(26)

The module must be enabled before it can be triggered.

# 6.4.6 \* Read Module Number

A(0).F(6).Read

This produces bit pattern 0000 0000 0000 0001 1001 1100 on the CAMAC bus.

# 6.4.7 \* Read Status Register

A(1).F(0)

| Bit 1 | l=Enabled                      | O=Disabled       |

|-------|--------------------------------|------------------|

| Bit 2 | l=Internal Clock               | 0=External Clock |

| Bit 3 | 1=Mode 2                       | 0=Mode 1         |

| Bit 4 | l=Retrigger On                 | 0=Retrigger Off  |

| Bit 5 | <pre>l-Divide Clock by 1</pre> |                  |

| Bit 6 | l=Divide Clock by 10           |                  |

| Bit 7 | 1=Divide Clock by 100          |                  |

|       | •                              |                  |

Bits 8-24 0

The enabled bit shall go to logic 0 at the end of the timing cycle unless retrigger mode is selected

#### 6.4.8 \* Read Memory Address

A(2).F(0)

| Bit | 1  | Memory  | Address | Bit | 0 | (LSB) |

|-----|----|---------|---------|-----|---|-------|

| Bit | 2  | Memory  | Address | Bit | 1 |       |

| Bit | 3  | Memory  | Address | Bit | 2 |       |

| Bít | 4  | Memory  | Address | Bit | 3 |       |

| Bit | 5  | Memory  | Address | Bit | 4 |       |

| Bit | 6  | Memory  | Address | Bit | 5 |       |

| Bit | 7  | Memory  | Address | Bit | 6 |       |

| Bit | 8  | Memory  | Address | Bit | 7 |       |

| Bit | 9  | liemory | Address | Bit | 8 |       |

| Bit | 10 | Memory  | Address | Bit | 9 | (MSB) |

Bits 11-24 0

# 6.4.9 Set Number of Cycles

A(1).F(16).Write

O Recycle until module is disabled or reset 1-255 Normal recycle mode

Default of 0 on reset

Recycle data is on lines W1-W8 with LSB on W1

#### 6.4.10 \* Reset

C+Z+Power On

Note: Only those dataway functions marked with a \* shall be accepted during the timing cycle; all others shall be ignored. The X line shall be a logic l whenever the module is provided with one of the